# Linearizability on hardware weak memory models

Graeme Smith

Kirsten Winter

Robert J. Colvin

School of Information Technology and Electrical Engineering, The University of Queensland, Australia

Abstract. Linearizability is a widely accepted notion of correctness for concurrent objects. Recent research has investigated redefining linearizability for particular hardware weak memory models, in particular for TSO. In this paper, we provide an overview of this research and show that such redefinitions of linearizability are not required: under an interpretation of specification behaviour which abstracts from weak memory effects, the standard definition of linearizability is sound and complete on all hardware weak memory models. We prove our result with respect to a definition of object refinement which takes a weak memory model as a parameter. The main consequence of our findings is that we can leverage the range of existing techniques and tools for standard linearizability when verifying concurrent objects running on hardware weak memory models.

Keywords: Linearizability: Correctness: Concurrent objects

# 1. Introduction

Linearizability [HW90] is a widely accepted notion of correctness for concurrent objects [MS04] that relates the behaviours of an object's implementation to the possible behaviours of its specification. As a correctness notion it benefits greatly from being *compositional*, i.e., the linearizability of each object of a system in isolation guarantees that the overall system is also linearizable. This provides us with a practical approach to proving correctness.

At the level of implementation, operations on an object take time and hence they may overlap in a multithreaded program. This is obviously difficult to reason about. Linearizability allows us to prove, however, that the behaviour of such an object implementation is consistent with that of a specification in which operations are atomic, and hence cannot overlap. The key concept is the notion of a *linearization point*, a point where an operation in the implementation can be thought of as taking effect atomically. Choosing

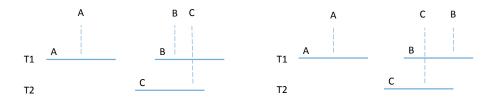

Fig. 1. Linearizability example

such a point for each operation in a concurrent history of an implementation allows us to match that history with a sequential history of the specification. The sequential history is referred to as a *linearization* of the concurrent history.

Figure 1 shows two linearizations of a concurrent history in which operation B of thread T1 overlaps with operation C of thread T2. There are two important things to note. Firstly, the linearization point of an operation must occur somewhere between its *invocation*, i.e., when it is called, and its *response*, i.e., when it returns. This means that operations which do not overlap in the concurrent history occur in the linearization in the order they were invoked. Secondly, overlapping operations in the concurrent history may occur in either order in the linearization, regardless of the order of their invocations and responses. A concurrent history satisfies a specification, provided one of its possible linearizations is a history of the specification.

A concurrent object is considered correct when each of its *finite* histories linearizes with a sequential history of the specification. Hence, linearizability only checks safety properties of an object implementation, not liveness properties [GY11, SW17]. Since linearizability is compositional, we can prove the correctness of a system of interacting objects by showing each component object is linearizable with respect to its specification [HW90].

Recent work [BGMY12, GMY12, TMW13, DSD14, DD16, DJRA18, DDWD18] examines the applicability of linearizability in the context of weak memory models of modern multicore architectures [SSO+10, SSA+11, MHMS+12, AFI+08, AMT14, FGP+16, CS18]. These memory models improve hardware efficiency by reducing accesses to global memory. Individual threads may operate on local copies of global variables, updates to the global memory being made by the hardware and largely out of the programmer's control. This can cause threads executing on different cores to get out of sync with respect to the values of global variables.

For example, on the TSO (Total Store Order) architecture [SSO $^+$ 10] a thread updating a global variable x stores the new value in a per-core FIFO buffer. Threads executing on that core will then read x from the buffer, rather than the global memory, until the new value is flushed from the buffer by the hardware. In the meantime, threads on other cores read the value of x from the global memory or from their own core's buffer when it has a value for x.

There have been several attempts at defining linearizability for TSO. Burckhardt et al. [BGMY12] include a notion of buffers in the specification of a concurrent object, and associate two atomic steps with each specification operation: one where the effect of the operation updates the buffer, and a subsequent one where it takes effect in the global memory. Gotsman et al. [GMY12] introduce nondeterminism into the specification to model that a thread may, or may not, have seen a recent update. Both of these approaches change the specification that the implementation needs to satisfy. The resulting specifications are less intuitive and do not correspond to specifications that would normally be found as part of a software library.

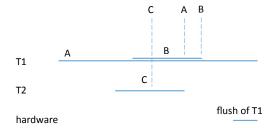

Derrick et al. [DSD14] take a different approach, leaving the specification unchanged and instead changing the definition of linearizability. A similar approach is used by Travkin et al. [TMW13, TW14] when developing tool support for proving linearizability on TSO. These approaches (which we will collectively call *TSO-linearizability*) change the bounds within which the linearization point must occur. Specifically, they do not require that the linearization point of an operation occurs before its response; it can occur any time up to the final flush associated with the operation. This could allow operation A of Figure 1 to linearize after C in the case when its flush occurs after C (see Figure 2).

TSO-linearizability is the basis for the proof methods in [DSGD14] and [DSGD17]. As proved in [DS15]

<sup>&</sup>lt;sup>1</sup> A programmer can add fences (or memory barriers) to code to force any pending updates to be written to memory. However, if used indiscriminately, fences reduce the gains in efficiency that a weak memory model provides.

Fig. 2. Linearizability example on TSO

| T1           | T2           |

|--------------|--------------|

| o.WriteX;    | o.WriteY;    |

| z := o.ReadY | w := o.ReadX |

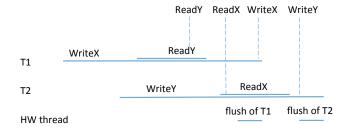

Fig. 3. Program that can result in z = w = 0 on TSO

it is compositional. It takes a particular view on the meaning of a specification in which, although operations occur atomically, they do not necessarily take effect immediately. Assume, for example, we have an object o with operations WriteX which writes value 1 to a variable x, WriteY which writes value 1 to a variable y, and ReadX and ReadY which read the variables x and y respectively. When a straightforward implementation of o's operations (i.e., one not involving fences) is run on TSO, the program in Figure 3 could result in both z and w being equal to 0 (the initial value of both variables). This occurs when the flushes of both writes are delayed until after both reads have executed. This somewhat surprising behaviour is considered correct by TSO-linearizability since there is a linearization as shown in Figure 4.

While this is a valid view of correctness, it requires the user to have a solid understanding of the memory model in order to know what behaviour the object might engage in. In particular, as can be seen in Figure 4, operations may effectively occur out-of-order with respect to *program order*, i.e., the order they appear in the program text. Under simple memory models like TSO, this is not too much of a burden for the user, but may become so under more complex memory models, especially when the code of the object also becomes more complex.

Strengthening the definition of TSO-linearizability to ensure that events take effect in program order is proposed in [DS15] and [DDGS15]. Under these definitions, the program in Figure 3 should never result in both z and w equal to 0 if the operations behave according to their specification. While this overcomes the above problem, it introduces a different one: the definition is no longer compositional. To see this, consider the example in Figure 5 where o1 and o2 are different objects with an operation Write (to write a local variable of the object) and an operation Read (to read the local variable).

Assume the implementation of each object (when run in isolation) is linearizable. When the objects are run together, compositionality would ensure that the combined system is also linearizable. However, the composed system of Figure 5 can result in both x and y being set to 0 on TSO. This is possible since T2 may perform its write to o2 and read from o1 before T1 writes to o1 (thus setting x to 0), but not flush the value it wrote to o2 until after the other two threads have run to completion (setting y to 0).

This outcome is not possible, however, according to a specification based on operations taking effect in

Fig. 4. Linearization of the program of Figure 3

Fig. 5. Compositionality counter-example (triangular race)

program order: if x is set to 0 then this step and hence the write to o2 on T2 must have taken effect before the write to o1 on T1 took effect, and hence before the read of o2 on T3. Hence, the composed system is not linearizable.

Doherty and Derrick [DD16] provide a variant of TSO-linearizability which preserves program order and is proved compositional when the client program is restricted to be free from *operation races* (like data races but at the level of operations rather than individual lines of code). The program in Figure 5 provides an example of such a racy program showing a *triangular race* [Owe10] and hence Doherty and Derrick's approach is not applicable. While their result is a useful contribution, it does not allow us to prove linearizability of objects which may be used in *any* context: something we would like for objects in a software library.

What is central to the quest to defining a suitable notion of linearizability is a reference point for correctness under weak memory models that allows one to prove soundness and completeness. What does it mean for an object implementation to behave correctly, and which behaviour of an object can be deemed incorrect? The answer to this seemingly simple question requires some attention in the context of weak memory models. In [SWC18] we provided such a notion of correctness, object refinement, which is based on a notion of trace refinement where the object is viewed in the context of a client program. This notion is similar to contextual or observational refinement [DG16, FORY10] but is geared for the context of weak memory models. Object refinement is parameterised by the memory model it refers to, and is therefore generic and can be instantiated for any hardware weak memory model. In this work we utilise this notion to provide a formal proof of soundness and completeness. In contrast to all previous work, we prove that using standard linearizability (as originally proposed by Herlihy and Wing [HW90]) is sound and complete not just on TSO, but any hardware weak memory model. It is, of course, also compositional (as proved by Herlihy and Wing).

To do this, we adopt an alternative view of a specification in which its operations occur and take effect atomically (rather than potentially taking effect later). This view of specifications has two advantages. Firstly, it ensures that an implementation maintains the *intent* of the specification, e.g., an implementation of a lock operation does not have a delayed effect that allows multiple threads to acquire the associated lock [DSD14]. Secondly, understanding a linearizable object's specified behaviour within a program does not require a knowledge of the memory model. Analogously to a specification of a concurrent object abstracting from the effects of interleaving, the specification in this view also abstracts from the effects of weak memory models.

The paper is structured as follows. In Section 2 we outline the basic concepts of our theory including that of  $effects^2$  which is key to our definitions. Based on these concepts, Section 3 formalises the semantics of programs under a given memory model and postulates some basic axioms that we assume of program behaviour under weak memory. The semantics of a concurrent object in the context of a client program, under a memory model, is elaborated in Section 4, distinguishing cases for the specification, in which operations are atomic, and the implementation which includes non-atomic, and possibly non-terminating, operations. Section 5 ties these basics into the notion of weak-memory trace refinement which defines refinement under memory model M for a client program using an object and its specification, respectively. The definition is parameterised with a given memory model for which we assume a semantics is given. Using weak-memory trace refinement we then define our notion of object refinement under memory model M which delivers the notion of correctness for objects. In Section 6, we prove that the standard definition of linearizability is both sound and complete with respect to our definition of object refinement. Section 7 illustrates how object refinement, and hence tracetallows traceta

Contributions. This paper is an extension of our previous paper [SWC18] in which our notion of object refinement was first defined. That paper provided a reference point from which definitions of linearizability

<sup>&</sup>lt;sup>2</sup> Referred to as *observations* in our earlier work [SWC18].

on different hardware weak memory models could be proved sound and complete. The definition of object refinement abstracts from the semantics of particular memory models, instead relying on an operational semantics, such as those for TSO [SSO+10] and the significantly weaker memory models POWER and ARM [FGP+16, CS18], to provide possible program behaviours. As it explicitly avoids out-of-thin-air results, it is not applicable to software weak memory models such as C11 [BOS+11, NMS16].

In this paper, we use that parameterised definition to show that standard linearizability is sound and complete for *all* hardware weak memory models. The assumptions that are required for the proofs are made explicit as axioms of the program semantics. These axioms are derivable from concepts, like object encapsulation and atomicity, and are independent of weak memory model behaviour. This is in contrast to previous work which has changed the definition of linearizability, often for a specific memory model. Earlier in this section, we have provided an overview of this body of earlier work and related the different definitions.

The main consequence of our findings is that we can leverage the range of existing techniques and tools for standard linearizability when verifying concurrent objects running on hardware weak memory models.

# 2. Client programs and effect events

To investigate the behaviour of concurrent objects under hardware weak memory models, and relate their implementations to their specifications using refinement, we need to consider the calling context. Programs calling the operations of a concurrent object are referred to as *client programs*, or clients for short. A client program P is concurrent, running multiple threads  $T_i$  possibly on multiple cores, and is affected by the memory model of the architecture it is running on. For some finite n, we have<sup>3</sup>

$$P \stackrel{\widehat{=}}{=} T_1 \parallel T_2 \parallel \ldots \parallel T_n.$$

Following other work on concurrent objects [HW90, FORY10, DG16], the behaviour of a program is described in terms of *events* that occur. We allow events to be *program steps*, *operation events* or, as introduced in Section 2.1, *effect events*.

Program steps are any steps performed by the client other than calling an object operation. These are assignments, conditional branch instructions (e.g., if or while statements), other control instructions like various forms of fences, atomic read-modify-write instructions which atomically perform these three steps (e.g., the compare-and-swap instruction CAS), and higher-level instructions which can, in many cases, be defined in terms of assignments and/or conditional branches. For example, a statement await(z=1) could be defined as while(z  $\neq$  1) {}.

Operation events abstract the behaviour of an operation call by a program. They include the *invocation* of the operation (i.e., when it is called) and the operation's *response* (i.e., when it returns). The operation events carry the operation's input and output values as parameters and thus reflect the operation's externally visible behaviour. The internal behaviour of an object is elided.

# 2.1. Effect events

Central to our definitions is the notion of an *effect event*. Such an event denotes the point in an execution where a program step or an operation can be deemed to have taken effect and (if observable) has been observed by *all* threads  $T_i$  of client P. Effect events are where the results of program steps and output values of operations (if any) become known globally.

Note that an operation's internal steps and their effects are not observable on the program level (due to object encapsulation), and hence we record only one effect event per operation call. These operation effects are not used for object refinement. Object refinement is based on the refinement of the client program and only takes into account observable program steps. However, operation effects are essential when defining the semantics of objects in a context of a client running under a weak memory model, as we will see in Section 4.

Introducing effect events allows us to decouple when events occur in a program and when they are observed by other threads, which might not fall together under hardware weak memory models. Program steps and invocation and response events correspond to the points in an execution where the program counter

<sup>&</sup>lt;sup>3</sup> For simplicity, we do not consider dynamically spawned threads.

$$\begin{array}{lll} \text{T1} & \text{T2} \\ x := \text{o.A();} & \text{await(z=1);} \\ z := 1; & \text{o.C();} \\ \text{o.B();} & \end{array}$$

Fig. 6. Client program

(pc) is at the address of the corresponding instruction. For an invocation or response, this instruction will be an update to pc, setting it to where the execution should continue. Hence, for any memory model these events will remain in the order that they occur in the program text.

The semantics specific to the memory model under consideration determines the possible orderings of the effect events. Effect events occur only after their matching program event or, in the case of an operation, after the matching invocation. Furthermore, for any program step or operation that writes to memory, its effect will occur when all threads can either

- (a) access the new value of a global program variable written by a program step, or

- (b) access the values of all shared object variables written by an operation.

# 2.2. Programs

The behaviour of a concurrent program P under a weak memory model M can be described by a partial order  $<_{P_M}$  over the events of the program to which all possible executions of that program must adhere. When event e occurs before event e' in the partial order, i.e.,  $(e, e') \in <_{P_M}$  then event e must occur before event e' in any execution of P. When P involves branching (e.g., if or while statements), there will be several paths through P (one corresponding to each combination of branches). The events of different paths need to be distinct which can be ensured, for example, by including in each event an identifier of the path to which it belongs.

To understand what a partial order of a program for a particular memory model might look like consider the example of a client program given in Figure 6 with two global program variables x and z, running on two threads T1 and T2. The threads call three operations of the same object o, of which the operation B does not write to any shared object variable. Note that we assume that the result of any operation call is implicitly stored in a local register (e.g.,  $r_A$  for the operation call o.A), and  $inv_A$  denotes the invocation of o.A, etc.

On a sequentially consistent (SC) architecture, i.e., one without a weak memory model, writes to global variables occur instantaneously. Hence, the effect event for a program step occurs immediately after the program step, and that of an operation between its invocation and response. The partial order on the events of the program of Figure 6 on SC is shown below. The branch in the partial order after the program step z=1 of thread T1 takes effect corresponds to the operation call o.B() of T1 occurring in parallel with the code of thread T2.

$$\begin{array}{c} \text{inv}_{B} - \text{eff}_{B} - \text{res}_{B} \\ \text{inv}_{A} - \text{eff}_{A} - \text{res}_{A} - \text{x} = \text{r}_{A} - \text{eff}_{x = \text{r}_{A}} - \text{z} = 1 - \text{eff}_{z = 1} \\ \text{await}(z = 1) \\ \text{eff}_{await}(z = 1) \\ \text{inv}_{C} - \text{eff}_{C} - \text{res}_{C} \end{array}$$

On TSO [SSO<sup>+</sup>10], writes to global variables and shared object variables become available to threads on other cores when they are flushed. These flushes may occur at some later point, but we know that they occur in the same order as the writes occurred. Hence, in the partial order of the events on TSO (depicted below), eff<sub>A</sub> occurs before eff<sub>x=rA</sub> which occurs before eff<sub>z=1</sub>. The effect event eff<sub>B</sub> can only occur after inv<sub>B</sub> but is not ordered with respect to the other effect events since o.B does not write to any shared variable, and hence does not have to follow the FIFO order of flushes of writes. Similarly, the effect events eff<sub>await(z=1)</sub> and eff<sub>C</sub> are un-ordered.

On ARM and POWER [SSA+11, MHMS+12, AFI+08, AMT14, FGP+16, CS18], the effect events might occur out of (program-) order and also flushing of variables need not occur in a FIFO manner. Hence the effects are un-ordered in the partial order of the program depicted below, apart from  $eff_A$  and  $eff_{x=rA}$  which are ordered due to a data-dependency on register  $r_A$ . As under TSO, the assignment to z and the await statement maintain their order due to the data dependency (on z) and the synchronisation (await) between T1 and T2.

For programs with more than two threads, the semantics of ARM and POWER also allow non-multi-copy atiomicity, i.e., where threads on different cores to the thread performing a write may see the write at different times. On such a memory model, the effect will be the point where all cores have seen the write. In the operational semantics of ARM and POWER in [CS18], non-multi-copy atomicity is modelled using a sequence of writes where each write is associated with the set of thread identifiers of threads which have seen the write. The effect occurs in this semantics when that sequence indicates that all threads have seen either the write or a future write to the same variable, i.e., one that occurs later in the execution.

The order in which effect events occur in an actual behaviour of a program determines the value of the output associated with the effect. This value must also correspond to the output value of the operation response or program step that is observed through the effect event. This correspondence, which prevents out-of-thin air results available in software memory models such as C11 [BOS<sup>+</sup>11, NMS16], is captured in a well-formedness condition on traces formalised in the next section.

### 3. Semantics of programs relative to the memory model

The semantics of a program P under memory model M is defined in terms of the set of *events* that can occur, and a partial order  $<_{P_M}$  over those events. The events are, on one hand, determined by P through the program text, and, on the other hand, determined by the semantics of the memory model as outlined in Section 2. In this section, we formalise the semantics of a program assuming its events and partial order are given.

# 3.1. Events

Let T be the set of all thread identifiers, and Call the set of all (unique) operation calls. An operation is then defined as a call by a particular thread.

$$Op \stackrel{\frown}{=} T \times Call$$

Let PS denote the set of all program step events, and Val the set of all values (of input and output parameters), including a special element  $\bot$  meaning 'no value'. The set of all events is defined as follows, where each invocation is associated with an input, and each response and effect with an output.

$$\mathit{Event} \mathrel{\widehat{=}} \mathit{step}(\mathit{T}, \mathit{PS}) \mid \mathit{eff}(\mathit{T}, \mathit{PS}) \mid \mathit{inv}(\mathit{Op}, \mathit{Val}) \mid \mathit{res}(\mathit{Op}, \mathit{Val}) \mid \mathit{eff}(\mathit{Op}, \mathit{Val})$$

In the remainder of this paper, we refer to step(T, PS) and eff(T, PS) as program events, ProgEvents, and to inv(Op, Val), res(Op, Val), and eff(Op, Val) as object events, ObjEvents.

A program P has a set of events, events(P), such that for each invocation event in events(P), events(P) also contains all possible corresponding response and effect events. That is, each called operation can respond and take effect and the associated output is not under the program's control.

$$\forall op: Op; in: Val \bullet inv(op, in) \in events(P) \Rightarrow \forall out: Val \bullet \{res(op, out), eff(op, out)\} \subseteq events(P)$$

$$(1)$$

#### 3.2. Traces

The semantics of a program P is described as a set of *finite* sequences of events, referred to as traces.<sup>4</sup> In the following  $t_i$  denotes the ith element of a trace t, and #t its length.

For each trace t, each event is unique (similar events, e.g., calls to the same operation, may be annotated by their relative position in the trace).

```

Trace = \{t : \text{seq } Event \mid \forall i, j \leq \#t \bullet i \neq j \Rightarrow t_i \neq t_j\}

```

The events of a trace and the order on these events are defined as follows.

```

events(t) = \{a : Event \mid \exists i \leq \#t \bullet t_i = a\}<_t = \{(a, b) : Event \times Event \mid \exists i, j \leq \#t \bullet i < j \land t_i = a \land t_j = b\}

```

Note that the order  $<_t$  is a total order over the events in t, as a trace describes exactly one execution of a program.

As a well-formedness condition on traces we postulate that an invocation of an operation always occurs before both the associated response and the associated effect. Similarly, a program step always occurs before its effect. Also, the output value of an operation's effect is the same as that of the corresponding response event. For any trace t we have

```

(\forall a: Op; out: Val \bullet (\forall j \leq \#t \bullet t_j \in \{res(a, out), eff(a, out)\} \Rightarrow \exists in: Val; i < j \bullet t_i = inv(a, in))) \land (\forall s: T; p: PS \bullet (\forall j \leq \#t \bullet t_j = eff(s, p) \Rightarrow \exists i < j \bullet t_i = step(s, p))) \land (\forall a: Op; out_r, out_e: Val \bullet \{res(a, out_r), eff(a, out_e)\} \subseteq events(t) \Rightarrow out_r = out_e)

(2)

```

Since responses remain in the order they appear in the program text, the constraint on the outputs of effects and responses prevents out-of-thin-air results.

# 3.3. Programs

The semantics of program P on memory model M is defined as the set of traces using only events from P and whose orders adhere to the constraints prescribed by the partial order  $<_{P_M}$ . That is, if a pair of events (a,b) is in  $<_{P_M}$  and b is in an execution of P on M then a occurs earlier in that execution. Hence the semantics of P on M is defined as

```

[\![P]\!]_M \cong \{t : Trace \mid events(t) \subseteq events(P) \land <_{P_M} \in <_t \}

```

where  $<_{P_M} \in <_t$  specifies whether an order is allowed by P on M, formally defined as

$$<_{P_M} \in <_t \ \widehat{=} \ \forall (a,b) : <_{P_M} \bullet b \in events(t) \Rightarrow (a,b) \in <_t$$

That is, for any event b that occurs in trace t, if this event is constrained to come after another event a by  $<_{P_M}$ , then event a must also occur in t before event b. Note that it is not suitable to use the simple subset relation here, i.e.,  $<_{P_M} \subseteq <_t$ , since trace t will not, in general, include all events b that are constrained by  $<_{P_M}$ .

$<_{P_M}$ . Since we are aiming at the most general description of program semantics under any memory model, we do not explicitly prescribe  $<_{P_M}$ . Instead, based on the understanding of concurrent programs, concurrent objects and their interplay (as laid out in Section 2), we formulate certain characteristics of  $<_{P_M}$  that are shared by all memory models, and provide a set of axioms in the remainder of this section.

<sup>&</sup>lt;sup>4</sup> Since we are interested in defining a notion of correctness that readily relates to linearizability, and hence only safety properties [GY11, SW17], we do not consider infinite sequences of events in our semantics.

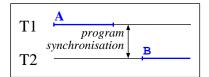

Fig. 7. Scenarios of synchronisations between threads

In the context of this work, we are interested in both the order of operation events and the order between operation and program events in  $<_{P_M}$ . We define synchronisation (between threads) as an event on one thread affecting the occurrence of another event on another thread. Synchronisation requires a writing and a reading access to a shared variable (e.g., through an await statement or a conditional). We make the following assumptions on objects and clients:

- The state space of an object is encapsulated and hence the client does not share any variables directly with the object; communication occurs only through input and output values of the object's operations.

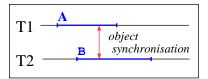

- Consequently, synchronisation between two threads can only occur between program events (referred to as program synchronisation) or between operation events (referred to as object synchronisation). The client cannot directly synchronise with a step in an operation that occurs between its invocation and response, but only with the invocation and response events themselves which serve as the interface between client and object. Figure 7 depicts the possible synchronisations by means of two scenarios: The scenario on the left illustrates program synchronisation between the threads T1 and T2, in which the program synchronises on two program steps which follow operation A and precede operation B, respectively. An example of this type of synchronisation is given by the instructions z=1 and await(z=1) in Figure 6. The scenario on the right illustrates operations A and B overlapping and synchronising on the object level, outside the control of P.

- A client cannot enforce a flush within an operation; the operation's implementation is outside the client's control.

From these assumptions we can deduce that  $<_{P_M}$  can only enforce the invocation of an operation to occur before another event, which is not the effect of the operation<sup>5</sup>, if and only if the response is also enforced to occur before the event. (The implication from right to left holds due to the well-formedness condition (2).)

$$\forall e, inv(a, in), res(a, out) : events(P) \bullet e \neq eff(a, out) \Rightarrow ((inv(a, in), e) \in \langle P_M \Leftrightarrow (res(a, out), e) \in \langle P_M \rangle)$$

(3)

Similarly,  $<_{P_M}$  cannot enforce the response of an operation to come *after* another event, which is not the effect of the operation, unless it also enforces the invocation to come after the event. (As above, the implication from right to left holds due to well-formedness (2).)

$$\forall e, inv(a, in), res(a, out) : events(P) \bullet e \neq eff(a, out) \Rightarrow ((e, res(a, out)) \in \langle P_M \Leftrightarrow (e, inv(a, in)) \in \langle P_M \rangle)$$

$$(4)$$

A similar condition holds for the order of effect events with respect to program events. Due to an object's implementation, the effect of an operation might occur before its response event (e.g., if the operation is implemented with fence instructions which prevent a delay in its effect), which is outside the control of P. Hence  $<_{P_M}$  cannot enforce the effect of an operation to come *after* another *program* event unless it also enforces the invocation to come after the program event. (Again, the implication from right to left holds due to well-formedness (2).)

$$\forall e, inv(a, in), eff(a, out) : events(P) \bullet e \in \mathcal{P}rogEvents \Rightarrow ((e, eff(a, out)) \in \langle P_M \Leftrightarrow (e, inv(a, in)) \in \langle P_M \rangle)$$

$$(5)$$

In some memory models, the order in which two effects can occur can be constrained (e.g., in TSO the order of observable effects follows the order of the observed events), but only if the order of the corresponding

<sup>&</sup>lt;sup>5</sup> The other event can be the response of the operation since partial orders are reflexive and hence (res(c), res(c)) is in  $<_{P_M}$  for any c.

events is also enforced. Any order that is caused by the nature of a particular implementation (e.g., an additional fence instruction in the code) is outside the control of P (similarly to the case above). This means, if the effects of two operations are ordered then the order of the operations must be enforced, and hence the response of one operation must occur before the invocation of the other.

```

\forall \ inv(a,in), eff(a,out), res(c), eff(c): events(P) \bullet \\ ((eff(c), eff(a,out)) \in <_{P_M} \land c \neq (a,out)) \Rightarrow (res(c), inv(a,in)) \in <_{P_M}

```

A similar condition holds if  $<_{P_M}$  enforces an operation effect to occur after the invocation, response or effect event of another operation. This is only possible if the two operations are ordered (and hence the response of the first must occur before the invocation of the other). If the operations are not ordered by  $<_{P_M}$ , they may occur in either order (and hence the effects may occur in either order) or they may overlap. For overlapping operations,  $<_{P_M}$  cannot enforce an order of object events since any object synchronisation is beyond the control of P. Therefore we can generalise the above axiom as follows.

```

\forall inv(a, in_a), res(a, out_a), eff(a, out_a), inv(b, in_b), eff(b, out_b) : events(P) \bullet

\forall e : \{inv(a, in_a), res(a, out_a), eff(a, out_a)\} \bullet

((e, eff(b, out_b) \in \langle P_M \land a \neq b) \Rightarrow (res(a, out_a), inv(b, in_b)) \in \langle P_M \rangle )

(6)

```

As a consequence of these observations we deduce that an order between object events of two operations can only be enforced by  $<_{P_M}$  if  $<_{P_M}$  also enforces that these two operations do not overlap.

# Lemma 1 (Enforced ordering on object events).

```

\forall \ inv(a,in_a), \ res(a,out_a), \ eff(a,out_a), \ inv(b,in_b), \ res(b,out_b), \ eff(b,out_b): \ events(P) \bullet \\ \forall \ e: \{inv(a,in_a), res(a,out_a), \ eff(a,out_a)\}; \ \ e': \{inv(b,in_b), res(b,out_b), \ eff(b,out_b)\} \bullet \\ ((e,e') \in <_{P_M} \land \ a \neq b) \ \Rightarrow \ (res(a,out_a), inv(b,in_b)) \in <_{P_M}

```

The proof follows the simple application of Axioms (3) to (6) to all combinations of invocation, response and effect events of the two operations.

# 4. Semantics of objects under weak memory models

To define object refinement, our notion of correctness, in Section 5, we need to constrain the behaviour of a program to a particular object or collection of objects (called an *object system* in [FORY10]). In either case, the interface between the program and the one or more objects is the operations of those objects, the outputs of which, when the operations are called in a given sequence, reflect the objects' behaviour including any interactions between them. For ease of presentation, we consider a single object only, but the results also hold for a collection of interacting objects whose interface is the operations of all objects in the collection.

Let  $t_{|ir}$  denotes the trace t restricted to invocation and response events. The semantics of an object is given as a set of *histories*, where each history is a trace with only invocation and response events.

```

History = \{t : Trace \mid t_{|ir} = t\}

```

# 4.1. Object implementation under weak memory models

An object implementation C has a set of object events, events(C), and, on a particular memory model M, a prefix-closed set of histories made up of those events,  $[\![C]\!]_M$ .

For any object implementation C, P[C] denotes the object C operating in program P. It is only defined when all invocation events of P are events of C. The semantics of C operating in P on memory model M,  $[\![P[C]]\!]_M$ , is given as those traces of P on M whose object events correspond to a history of C on M.

$$[\![P[C]]\!]_M \ \widehat{=} \ \{t: [\![P]\!]_M \mid \exists \ h: [\![C]\!]_M \bullet t_{|ir} = h\}$$

$<sup>^{6}</sup>$  The set of histories of C would be derived in an operational manner based on the weak memory model semantics. This may involve two passes in which firstly effects and their placement are taken into account, and secondly response values are added to reflect this placement, and effects are discarded.

Fig. 8. Client program using lock

# 4.2. Object specification under weak memory models

An object specification A similarly has a set of invocation and response events, events(A), and a prefix-closed set of histories, [A] (where prefixes are restricted to complete histories [HW90] in which the final event cannot be an invocation). Since A represents a typical specification found in a software library, its set of histories is independent of the memory model (hence there is no subscript). Any weak memory model behaviour is absent from its histories due to its operations being atomic, i.e., they respond and take effect immediately and hence occur without interference from other operations. That is, every history in [A] is a sequence of invocation and response pairs, i.e., every invocation is followed by its response, and no overlapping of operations is possible.

```

\forall h : \llbracket A \rrbracket \bullet

(\forall i \leq \#h \bullet h_i = inv(a, in) \Rightarrow (i < \#h \land \exists out : Val \bullet h_{i+1} = res(a, out))) \land

(\forall i \leq \#h \bullet h_i = res(a, out) \Rightarrow (i \neq 1 \land \exists in : Val \bullet h_{i-1} = inv(a, in)))

(7)

```

To capture atomicity of specifications in our semantics, the behaviour of a client using specification A is restricted to those traces where only one operation is active at a time. For example, suppose the specification of a lock object, lock, has an operation acquire which waits until the value of a variable of the object, x, is 1 and sets it to 0, i.e., acquire is specified as await(x=1); x=0. Assuming x is initially 1, in the program of Figure 8 the intention would be that only one of y or z would be set to 1.

On SC, this intention is achieved when the invocation of acquire which occurs second does not happen until after the first acquire has taken effect. On TSO and assuming T1 and T2 are running on different cores, the intention is achieved when the invocation of acquire which occurs second does not happen until after the flush of x from the acquire which occurs first. This flush might be delayed. On ARM and POWER (again assuming T1 and T2 are on different cores), the intention is achieved when the second invocation of acquire does not happen until after the write to x by the first invocation has been seen by all threads (see description of non-multi-copy atomicity in Section 2.1).

In all cases, the intention is met when the second occurrence of acquire is not invoked before the effect event of the first occurrence. In general, for any object specification to behave as intended within a client context, an operation invocation does not occur before the effect event of a previously invoked operation. (Note that due to Axiom (7) invocations also must occur after responses of a previous operation.)

Provided all invocation events of a program P are events of a specification A, P[A] denotes the program P operating with an abstract object whose behaviour satisfies A. To model atomicity, operations can only be invoked after previous operations have taken effect (as motivated above). The semantics of P[A] is given as follows.

# 5. Object refinement

Correctness of an object is defined from the client program's point of view. Such a program can only observe changes to program variables, i.e., variables that are not defined locally on a thread or as part on an object. Let  $t_{|global}$  denote the observable behaviour of a trace t, i.e., the sequence of effect events of program steps which write to global program variables. If for two traces t and t' we have  $t_{|global} = t'_{|global}$ , we call them matching traces.

A program P using C on memory model M refines P using A on M when any observable behaviour of the former is a possible observable behaviour of the latter, i.e., each concrete trace has a matching abstract trace. We refer to this property as weak-memory trace refinement.

**Definition 1.** Weak-memory trace refinement

$$P[A] \sqsubseteq_{M} P[C] \ \widehat{=} \ \forall \ t : \llbracket P[C] \rrbracket_{M} \bullet \exists \ t' : \llbracket P[A] \rrbracket_{M} \bullet \ t' \mid_{global} = t \mid_{global}$$

An object implementation C refines an object specification A under weak memory model M if for all possible client programs P, P using C weak-memory trace refines P using A under memory model M. We refer to this property as *object refinement*.

**Definition 2.** Object Refinement under memory model M

$$A \sqsubseteq_M C \ \widehat{=} \ \forall P \bullet P[A] \sqsubseteq_M P[C]$$

If  $A \sqsubseteq_M C$  we say that C is correct with respect to A under memory model M.

# 6. Linearizability

Linearizability relates histories of an object implementation, which may have pending invocations, i.e., invocations for which there is no response, to histories of an object specification which do not [HW90]. To do this, it needs to complete the implementation histories. This can be done by adding a response when a pending invocation is deemed to have taken effect, and removing the invocation when it has not [HW90]. For example, consider a history comprising a read operation of a variable x occurring on a thread T1 concurrently with a write operation to x on thread T2 where the latter has not yet responded. If the read operation returns the value from the write operation, we can assume the write operation has taken effect and hence we add a response to the history. If the read operation returns the value of x from before the write operation, we can assume the latter has not taken effect and remove its pending invocation.

To define linearizability, functions are put in place for adding responses, and removing invocations from histories. The function *ext* returns the set of traces which extend a given trace with a sequence of responses such that the result is still a trace, i.e., responses are only added for pending invocations.

$$ext(t) \triangleq \{t \land tr : Trace \mid \forall i \leq \#tr \bullet \exists c : Op \times Val \bullet tr_i = res(c)\}$$

The function *comp* returns the trace resulting from the removal of all invocations from a given trace which have neither an effect nor a response.

$$comp(t) \stackrel{\triangle}{=} \left\{ \begin{array}{l} \langle \, \rangle, & \text{if } t = \langle \, \rangle \\ comp(tail\,t), & \text{if } NoResp(t) \\ \langle head\,t \rangle \, \widehat{} \, comp(tail\,t), & \text{otherwise} \end{array} \right.$$

```

where NoResp(t) = \exists a : Op; in : Val \bullet head(t) = inv(a, in) \land \nexists out : Val; i \leq \#t \bullet t_i \in \{res(a, out), eff(a, out)\}

```

The following formalisation of the standard definition of linearizability is based on that of Derrick et al. [DSW11] which has been proved to correspond to the original definition by Herlihy and Wing [HW90]. (Note that  $comp(h^+)$  removes all pending invocations from  $h^+$  since histories do not have effect events.)

**Definition 3.** Linearizability (standard definition)

$$C \hspace{0.1cm} \operatorname{lin}_{M} \hspace{0.1cm} A \hspace{0.1cm} \widehat{=} \hspace{0.1cm} \forall \hspace{0.1cm} h : [\![C]\!]_{M} \hspace{0.1cm} \bullet \hspace{0.1cm} \exists \hspace{0.1cm} h' : [\![A]\!] \hspace{0.1cm} \bullet \hspace{0.1cm} \exists \hspace{0.1cm} h^{+} : \operatorname{ext}(h) \hspace{0.1cm} \bullet \hspace{0.1cm} \operatorname{comp}(h^{+}) \sim h' \wedge \prec_{\operatorname{comp}(h^{+})} \subseteq \prec_{h'}$$

where  $t \sim t'$  denotes that t and t' are thread equivalent, i.e., when restricted to the events of any one thread they have the same sequence of invocations and responses, and  $\prec_t = \{(res(c), inv(d)) : <_t\}$ , i.e.,  $\prec_t$  captures the order between operations in a trace (where an operation comes before another if its response is before the other's invocation).

<sup>&</sup>lt;sup>7</sup> In this case, we could also add a response since the write could have taken effect, but after the read took effect. However, to be consistent with the original definition of linearizability, we allow invocations to be removed.

The intuition behind the definition is that operations which are overlapping in  $comp(h^+)$  are not ordered by  $\prec_{comp(h^+)}$  and, with  $\prec_{h'}$  being a superset of  $\prec_{comp(h^+)}$ , can occur in any order in h'. For example, the overlapping operations B and C of the implementation history of Figure 1 can occur in any order in a linearization of that history. This is equivalent to letting the linearization points of B and C occur anytime between the respective operations' invocations and responses.

Importantly, the definition is compositional (this property is proved for the above definition by Herlihy and Wing who refer to it as locality [HW90]). In the case when the object implementation C is a collection of interacting objects, compositionality allows us to prove that C is linearizable to a specification of a similar collection of interacting objects by proving each individual object implementation is linearizable to the corresponding object specification.

In the remainder of this section, we prove that standard linearizability is sound and complete with respect to our definition of object refinement. To facilitate the proofs, we introduce the following lemmas on completions of traces whose proofs are included in Appendix A.

**Lemma 2.** If the events of a trace t are events of a program P then so are the events of any completion of t

```

\forall P \bullet \forall t : Trace \bullet \forall t^+ : ext(t) \bullet events(t) \subseteq events(P) \Rightarrow events(comp(t^+)) \subseteq events(P)

```

**Lemma 3.** If a trace t is allowed by a program P on memory model M then so is any completion of trace t that only adds responses for operations whose effects have occurred.

```

\forall P, M \bullet \forall t : Trace \bullet \forall t ^ tr : ext(t) \bullet (\forall i \leq \#tr; \ c : Op \times Val \bullet tr_i = res(c) \Rightarrow \exists j \leq \#t \bullet t_j = eff(c)) \land <_{P_M} \in <_t \Rightarrow <_{P_M} \in <_{comp(t \land tr)}

```

**Lemma 4.** The operation order of a completion of a trace t is a subset of that of t.

```

\forall t : Trace \bullet \forall t^+ : ext(t) \bullet \prec_{comp(t^+)} \subseteq \prec_t

```

# 6.1. Soundness

The soundness of standard linearizability in the context of weak memory model M can now be proved in relation to our notion of object refinement under M.

**Theorem 1.** If an object implementation C linearizes with an object specification A on memory model M then for all client programs P, P[C] is a weak-memory trace refinement of P[A] on M.

$$C \lim_M A \Rightarrow \forall P \bullet P[A] \sqsubseteq_M P[C]$$

The proof of this theorem takes any concrete history h of C and any abstract history h' of A, where the latter is a linearization of the former, and any trace t of a program calling C that corresponds to the concrete history h. From these ingredients we construct an abstract trace t' such that t' corresponds to the linearization h'. That is, we move the object events of t such that the operations do not overlap and also occur in the same order as in h' in the resulting trace t'. It then remains to show that the trace that is constructed in this way is indeed a trace of the client calling the abstract object (i.e., that t' is a trace of P[A]).

# Proof

Expanding  $\lim_{M}$  and  $\sqsubseteq_{M}$  we have

```

(\forall h : [\![C]\!]_M \bullet \exists h' : [\![A]\!] \bullet \exists h^+ : ext(h) \bullet comp(h^+) \sim h' \land \prec_{comp(h^+)} \subseteq \prec_{h'}) \Rightarrow \forall P \bullet \forall t : [\![P[C]\!]\!]_M \bullet \exists t' : [\![P[A]\!]\!]_M \bullet t'_{|global} = t_{|global}

```

We need to prove that the consequent holds whenever the antecedent does. For any P, either  $[P[C]]_M = \emptyset$

and the consequent trivially holds, or there exists a trace t in  $[P[C]]_M$ . In the latter case, we have that there exists an h in  $[C]_M$  such that  $t_{|ir} = h$  (from the definition of  $[P[C]]_M$ ).

Given such a t and h, when the antecedent holds we also have an  $h' \in [A]$  and an  $h^+ \in ext(h)$  such that

$$comp(h^+) \sim h' \wedge \prec_{comp(h^+)} \subseteq \prec_{h'}$$

(S1)

There may be a number of choices for  $h^+$  based on how many pending invocations are given responses. We choose  $h^+$  so that there is an added response for exactly those pending invocations whose effects occur in t. This is always possible since we know that there exists at least one extension and related abstract history. Call them  $h_0^+$  and  $h_0'$ , respectively.  $h_0^+$  cannot have less than the required responses. If it did,  $comp(h^+)$  would be left with a pending invocation (with an effect) but no response. Hence,  $comp(h^+) \sim h'$  would not hold. If  $h_0^+$  has more than the required responses, since  $[\![A]\!]$  is prefixed-closed, we can find an h' which is a subsequence of  $h_0'$  which does not have the additional operations corresponding to the extra responses. This h' will satisfy (S1) for our chosen  $h_0^+$ .

This h' will satisfy (S1) for our chosen h+. Since  $t \in [\![P[C]]\!]_M$ , we can deduce from the definition of  $[\![P[C]]\!]_M$  that  $t \in [\![P]\!]_M$ , and with the definition of  $[\![P]\!]_M$ , we have that

$$events(t) \subseteq events(P) \land <_{P_M} \in <_t$$

(S2)

Let  $t^+ \in ext(t)$  be the trace that extends t with the same sequence of responses that  $h^+$  extends h. It follows that

$$t^{+}_{|ir} = h^{+} \wedge comp(t^{+})_{|ir} = comp(h^{+})$$

(S3)

From (S2), Lemma 2 and Lemma 3 (and since we choose  $h^+$  to only add responses to h for operations whose effects occur in t) we have

$$events(comp(t^+)) \subseteq events(P) \land <_{P_M} \in <_{comp(t^+)}$$

(S4)

Since  $t^{+}_{|ir} = h^{+}$  (S3) and  $comp(h^{+}) \sim h'$  (S1) we can deduce that

$$comp(t^+|_{ir}) \sim h'$$

(S5)

Central to our proof is the fact that we can construct the abstract trace t' appearing in the consequent of the theorem from trace  $comp(t^+)$  and history h'. This is done by means of a transformation function trans, which reorders object events in  $comp(t^+)$  to match the order in h', while maintaining the order of program events. We let  $t' = trans(comp(t^+), h', \langle \rangle)$  using the following definition of the transformation function.

**Definition 4 (Transformation function).** Let  $a \in Op$  be an operation,  $in, out \in Val$  be inputs and outputs, and  $r \in seq \mathcal{O}bjEvents$  a (remainder) sequence that temporarily stores invocations which will be placed into the resulting trace at a later point. The latter allows the invocations in the original trace to be reordered in the resulting trace.

Then trans(t, h', r) is equal to either

- (T1)  $\langle inv(a, in), eff(a, out), res(a, out) \rangle \cap trans(tail\ t, tail(tail\ h'), r)$ if  $head\ t = head\ h' = inv(a, in) \land \exists\ i \le \#t \bullet t_i = res(a, out),$

- (T2)  $trans(tail\ t, h', r \cap \langle inv(a, in) \rangle)$  if  $head\ t = inv(a, in) \wedge head\ h' \neq inv(a, in)$ ,

- (T3)  $trans(tail\ t, h', r)$  if  $head\ t \in \{res(a, out), eff(a, out)\},$

- (T4)  $\langle head t \rangle \cap trans(tail t, h', r)$  if  $head t \in \mathcal{P}rogEvents \land \nexists i < \#r \bullet r_i = head h'$ , or

- (T5)  $\langle inv(a,in), eff(a,out), res(a,out) \rangle \cap trans(t, tail(tail h'), r \{inv(a,in)\})$ if  $\exists i \leq \#r \bullet r_i = head h' = inv(a,in) \land \exists i \leq \#t \bullet t_i = res(a,out).$

Note that (T1) - (T5) cover all cases when t has a response for each invocation (as  $comp(t^+)$  does). If the head of t is an invocation, it is either added to t' (along with the corresponding effect and a matching response) (T1) or added to t' (T2). If it is a response or effect, it is removed (T3). If it is a program event, and the head of t' is not in t', it is added to t' (Along with

<sup>&</sup>lt;sup>8</sup> Since there is at most one pending invocation per thread, such an h' will be in the prefix-closed set  $[\![A]\!]$ .

the corresponding effect and a matching response) (T5). Since  $comp(t^+|_{ir}) \sim h'$  (S5), all invocations added to r will eventually be processed via the recursive definition.

It is easy to prove that cases (T1) – (T5) of Definition 4 ensure that the newly constructed trace t' contains the same invocation and response events as  $comp(t^+)$  and its restriction to invocation and response events matches h'.

$$events(t'_{|ir}) = events(comp(t^+)_{|ir}) \wedge t'_{|ir} = h'$$

(S6)

Cases (T1) and (T5) in particular ensure that in the transformed trace the operations do not overlap (as invocations, effects and responses of each operation are added to t' in one step).

$$\forall c: Op \times Val; \ k \leq \#t' \bullet t'_k = inv(c) \Rightarrow \\ \forall a: Op; \ in: Val; \ i < k \bullet t'_i = inv(a, in) \Rightarrow \exists \ out: Val; \ j < k \bullet t'_j = eff(a, out)$$

(S7)

With case (T4) we also ensure that program steps are in the same order in t and t'.

$$t'_{|p} = t_{|p} \tag{S8}$$

where  $t_{\perp p}$  denotes the trace t restricted to program events. Hence, we have

$$t'_{|qlobal} = t_{|qlobal}$$

(S9)

To prove the consequent of Theorem 1 it remains to show that  $t' \in \llbracket P[A] \rrbracket_M$ . Given the definition of  $\llbracket P[A] \rrbracket_M$  and (S6) and (S7) this reduces to proving that  $t' \in \llbracket P \rrbracket_M$ , i.e.,  $t' \in \mathit{Trace}$ ,  $events(t') \subseteq events(P)$  and  $<_{P_M} \in <_{t'}$ .

i.)  $t' \in Trace$ :

With  $t \in \llbracket P[C] \rrbracket_M$  and Lemmas 2 and 3 it follows that  $comp(t^+) \in \llbracket P \rrbracket_M$  and hence is a Trace. With  $events(t'_{|ir}) = events(comp(t^+)_{|ir})$  (S6) and  $t'_{|p} = t_{|p}$  (S8) and the fact that effects are only added to t' to match existing responses ((T1) and (T5)), it follows that all events in t' are unique. Due to cases (T1) and (T5) it is guaranteed that the order of object events in t' is well-formed, i.e., for all inv(a, in) in t' we have  $inv(a, in) <_{t'} res(a, out) \land inv(a, in) <_{t'} eff(a, out)$ . From case (T4) it follows that the order of program events (program steps and their effects) is maintained in t', i.e., for all step(s, p) and eff(s, p) in t' we have  $step(s, p) <_{t'} eff(s, p)$ . From the above it can be deduced that since t is a well-formed trace, t' is also a well-formed trace, i.e.,

$$t' \in Trace$$

(S10)

ii.)  $events(t') \subseteq events(P)$ :

With  $events(comp(t^+)) \subseteq events(P)$  ((S2) and Axiom (1)) and  $events(t'_{|ir}) = events(comp(t^+)_{|ir})$  (S6) and  $t'_{|p} = t_{|p}$  (S8) and the fact that effects are only added to t' to match existing responses ((T1) and (T5)) and these are in events(P) due to Axiom (1), it follows that

$$events(t') \subseteq events(P)$$

(S11)

iii.)  $<_{P_M} \in <_{t'}$ :

To prove this property it must be ensured that  $\forall (a,b): <_{P_M} \bullet b \in events(t') \Rightarrow (a,b) \in <_{t'}$ . This property is split into the following four cases.

a.) The order between two program events that is enforced by  $\langle P_M \rangle$  is maintained in t'.

$$\forall a, b : \mathcal{P}rogEvents \bullet (a, b) \in <_{P_M} \land b \in events(t') \Rightarrow (a, b) \in <_{t'}$$

b.) If  $<_{P_M}$  enforces that a program event has to occur before an object event then this order is maintained by t'.

$$\forall p : \mathcal{P}rogEvents; \ e \in \mathcal{O}bjEvents \bullet (p, e) \in <_{P_M} \land e \in events(t') \Rightarrow (p, e) \in <_{t'}$$

c.) If  $<_{P_M}$  enforces that an object event has to occur before a program event then this order is maintained by t'.

$$\forall p : \mathcal{P}rogEvents; \ e \in \mathcal{O}bjEvents \bullet (e, p) \in <_{P_M} \land p \in events(t') \Rightarrow (e, p) \in <_{t'}$$

d.) The order between two object events that is enforced by  $\langle P_M \rangle$  is maintained in t'.

$$\forall a, b : \mathcal{O} bjEvents \bullet (a, b) \in <_{P_M} \land b \in events(t') \Rightarrow (a, b) \in <_{t'}$$

These four remaining properties on t' rely firstly on assumptions on  $<_{P_M}$  relating to constraints on object events that might be enforced by P and M, which were outlined in Section 3, and secondly on properties of trans relating to the order of program events in t' which can be deduced from Definition 4. The proofs are provided in Appendix B.

### 6.2. Completeness

**Theorem 2.** If we have an object implementation C and specification A such that, for all programs P, P[C] is a weak-memory trace refinement of P[A] on memory model M then C linearizes to A on M.

$$(\forall P \bullet P[A] \sqsubseteq_M P[C]) \Rightarrow C \operatorname{lin}_M A$$

The proof of this theorem is based on the notion of a "strongest" client program  $\widehat{P}$  for each implementation history h (the details of which are explained below). When such a strongest client program exists, the antecedent of the theorem implies  $\widehat{P}[A] \sqsubseteq_M \widehat{P}[C]$  and we use this fact to prove that there exists an  $h' \in \llbracket A \rrbracket$  such that h linearizes to h'. In the case that such a strongest client program does not exist, we show that either (i) the theorem is trivially true, or (ii) there must be an  $h' \in \llbracket A \rrbracket$  such that h linearizes to h'. Applying these arguments to all h in  $\llbracket C \rrbracket_M$  results in the theorem's consequent being true.

The strongest client program  $\hat{P}$  of a history h is one which

- 1. allows h to occur enforcing the order of its operations, and

- 2. records every invocation and response in a global variable without delay.

Property 1 requires that  $\widehat{P}$  enforces the order of operations (i.e., the response/invocation order) to be as in h. Although  $\widehat{P}$  cannot control the outputs of operations, if it calls the operations with the inputs in h the corresponding outputs will be possible (since h is an implementation history). For operations on a particular thread, the required order is enforced by  $\widehat{P}$ 's program order. For operations on different threads, it can be achieved using inter-thread program synchronisation where necessary. For example, if the implementation history h refers to two threads, n and m, and the response of OpA(x) on n occurs before the invocation of OpB(y) on m in h then  $\widehat{P}$  could be of the form

```

...; u := OpA(x); z := 1; ... || ...; await(z = 1); v := OpB(y); ...

```

where initially z = 0 and the elided parts of the program do not change z.

Property 2 can be achieved, for example, with  $\widehat{P}$  having global variables  $var_{inv}$  and  $var_{res}$  and every operation call OpA(x) on thread n which returns a value appearing in  $\widehat{P}$  as  $var_{inv} = (n, OpA, x)$ ; fence; y = OpA(x);  $var_{res} = (n, OpA, x)$ ; fence, and every operation call OpA(x) which doesn't return a value as  $var_{inv} = (n, OpA, x)$ ; fence; OpA(x);  $var_{res} = (n, OpA, \bot)$ ; fence. Note that the recording of invocations and responses using  $var_{inv}$  and  $var_{res}$  is decoupled from the actual operation invocations and responses, and hence interleaving of the recording events from different threads is possible.

It is not necessarily the case that matching traces of such a strongest client program have the same sequence of invocations and responses. This is due to the fact that an invocation might be recorded (via  $var_{inv}$ ) but the operation not (yet) called, or an invocation and response have occurred but the response is not yet recorded (recall that traces are prefix-closed). Nevertheless, for each abstract trace that matches a concrete trace we can always find another abstract trace that also matches the concrete trace and additionally has the same sequence of invocations and responses as the completed concrete trace.

**Lemma 5.** For an object implementation C which is an object refinement of a specification A under M, and any client program P that records every invocation and response of an operation without delay, we have

$$\begin{array}{l} \forall \ t: \llbracket P[C] \rrbracket_{M} \bullet (\exists \ t': \llbracket P[A] \rrbracket_{M} \bullet t_{\mid global} = t'_{\mid global}) \Rightarrow \\ \exists \ t'': \llbracket P[A] \rrbracket_{M} \bullet t_{\mid global} = t''_{\mid global} \wedge \exists \ t^{+}: ext(t) \bullet comp(t^{+})_{\mid ir} \sim t''_{\mid ir} \end{array}$$

The proof of this lemma is based on the prefix closure of traces and can be found in Appendix C.

#### **Proof** of Theorem 2

Expanding  $\lim_{M}$  and  $\sqsubseteq_{M}$  we have

$$(\forall \, P \bullet \forall \, t : \llbracket P[C] \rrbracket_M \bullet \exists \, t' : \llbracket P[A] \rrbracket_M \bullet \, t'_{\,\,|global} = t_{\,\,|global} \,) \Rightarrow \\ \forall \, h : \llbracket C \rrbracket_M \bullet \exists \, h' : \llbracket A \rrbracket \bullet \exists \, h^+ : ext(h) \bullet comp(h^+) \sim h' \wedge \prec_{comp(h^+)} \subseteq \prec_{h'}$$

Assuming the antecedent is true, we prove the consequent for any  $h \in [\![C]\!]_M$ . It will not be possible to construct a strongest client program for h when the synchronisation between two threads, added explicitly or via a fence, changes the behaviour of the operation occurring after the synchronisation. In the example above, if synchronising using z causes OpB(y) to result in a different output then the resulting program will not allow h to occur. This situation would arise, for example, on TSO where the effect of OpA(x) would necessarily occur before the effect of z=1 due to the FIFO order of the per-core buffer. In other words, there will be no strongest client program when the behaviour of one operation (OpB(y)) in the example relies on the effect of an earlier operation (OpA(x)) in the example) being delayed.

For such a h, there are two possibilities.

- (i) We can construct a program P such that P[C] has an observable behaviour not in P[A] due to the delayed effect in h (since a similar delayed effect is not possible in P[A]), i.e.,  $\exists P \bullet \exists t : \llbracket P[C] \rrbracket_M \bullet t_{|ir} = h \land \forall t' : \llbracket P[A] \rrbracket_M \bullet t'_{|global} \neq t_{|global}$ . In this case, the antecedent of the theorem does not hold, and the theorem is trivially true.

- (ii) We cannot construct such a program P and hence  $\forall P \bullet \forall t : \llbracket P[C] \rrbracket_M \bullet t_{|ir} = h \Rightarrow \exists t' : \llbracket P[A] \rrbracket_M \bullet t'_{|global} = t_{|global}$ . In this case, consider a program  $P_0$  which allows the history h to occur, and indicates (for any other history) when the operations occur in the same order as in h by means of triangular races. For the example with OpA and OpB,  $P_0$  is of the form

$$z = 1; || ...; u = OpA(x); w = z; ... || ...; await(z = 1); v = OpB(y); ...$$

where z is initially 0 and the elided parts of the program do not change z, w or v. If  $P_0$  results in w=0, we can deduce that OpA(x) has occurred before OpB(y). Assume OpB(y) in C returns 1 when OpA(x)'s effect has taken place and 0 otherwise. For history h, the program  $P_0[C]$  will additionally result in v=0 since the effect of OpA(x) is delayed. Since we know there is an abstract trace t' matching each concrete trace t where  $t_{|ir} = h$ , it must be possible to have the result w = v = 0 from  $P_0[A]$ . Therefore, there must be a history  $h' \in [A]$  in which OpA(x) occurs before OpB(y) and the latter operation outputs 0 (even though the effect of OpA(x) is not delayed). This history h' is a linearization of h. Hence the consequent of the theorem holds for h.

For all other  $h \in [\![C]\!]_M$ , a strongest program  $\widehat{P}$  can be constructed. From Property 1, we know that  $\widehat{P}$  allows h to occur, i.e., there exists a trace of  $\widehat{P}[C]$  corresponding to h, and that  $\widehat{P}$  enforces the operations to occur in the order in h.

$$\exists t : [\widehat{P}[C]]_M \bullet t_{|ir} = h \tag{C1}$$

$$\forall c, d: Op \times Val \bullet (res(c), inv(d)) \in \langle c_h \Rightarrow (res(c), inv(d)) \in \langle c_h \rangle$$

(C2)

With Lemma 5 and the antecedent of the theorem we can deduce that if a concrete trace has a matching abstract trace there always exists another matching trace which has the same invocations and responses.

$$\forall t : [\widehat{P}[C]]_{M} \bullet \exists t'' : [\widehat{P}[A]]_{M} \bullet t_{|global} = t''_{|global} \land \exists t^{+} : ext(t) \bullet comp(t^{+})_{|ir} \sim t''_{|ir}$$

(C3)

Let  $t \in [\widehat{P}[C]]_M$  be any trace satisfying (C1), i.e.,

$$t_{|ir} = h \tag{C4}$$

There exists an abstract trace  $t'' \in [\widehat{P}[A]]_M$  and a trace  $t^+ \in ext(t)$  such that the completion of  $t^+$  and the abstract trace share the same invocations and responses (from (C3)).

$$comp(t^+)_{|ir} \sim t''_{|ir} \tag{C5}$$

With Lemma 4, it follows that

$$\prec_{comp(t^+)} \subseteq \prec_t$$

(C6)

Since  $t'' \in [\widehat{P}[A]]_M$ , from definition of  $[\widehat{P}[A]]_M$  we have that  $t'' \in [\widehat{P}]_M$  and hence

$$events(t'') \subseteq events(\widehat{P}) \land <_{\widehat{P}_M} \in <_{t''}.$$

(C7)

and that there exists an  $h' \in [A]$  such that

$$h' = t''_{|ir} \tag{C8}$$

From (C2) and (C4) we have

$$\forall c, d: Op \times Val \bullet (res(c), inv(d)) \in \langle c, t \rangle (res(c), inv(d)) \in \langle c, t \rangle (C9)$$

and with Lemma 4 and the definition of  $\prec$

$$\forall c, d: Op \times Val, t^{+}: ext(t) \bullet (res(c), inv(d)) \in \langle comp(t^{+}) \Rightarrow (res(c), inv(d)) \in \langle \widehat{p}_{M} \rangle$$

(C10)

Since  $\langle P_M \rangle$  allows t'' (C7) and with the definition of  $\subseteq$

$$\forall \ c,d: Op \times Val \bullet (res(c),inv(d)) \in <_{\widehat{P}_M} \land inv(d) \in events(t'') \Rightarrow (res(c),inv(d)) \in <_{t''}$$

(C11)

From (C5) we know that  $\forall d : Op \times Val \bullet inv(d) \in events(comp(t^+)) \Rightarrow inv(d) \in events(t'')$  and hence from (C10) and (C11) we have

$$\forall c, d: Op \times Val \bullet (res(c), inv(d)) \in <_{comp(t^+)} \Rightarrow (res(c), inv(d)) \in <_{t''}$$

(C12)

which is  $\prec_{comp(t^+)} \subseteq \prec_{t''}$  and hence we also have

$$\prec_{comp(t^+)_{lir}} \subseteq \prec_{t''_{lir}}$$

(C13)

Since  $t^+ \in ext(t)$ , and  $h = t_{|ir|}$ , there exists a  $h^+ \in ext(h)$  such that

$$h^+ = t^+_{|ir} \tag{C14}$$

From (C14) and (C13), it follows that

$$\prec_{comp(h^+)} \subseteq \prec_{t''|_{ir}}$$

(C15)

and from (C8)

$$\prec_{comp(h^+)} \subseteq \prec_{h'}$$

(C16)

This is the second conjunct of the consequent. We now derive the first.

From (C8) and (C5) we have

$$comp(t^+)_{|ir} \sim h'$$

(C17)

and hence with (C14)

$$comp(h^+) \sim h'$$

(C18)

Thus conjoining (C18) and (C16) gives us

$$comp(h^+) \sim h' \wedge \prec_{comp(h^+)} \subseteq \prec_{h'}$$

(C19)

which is the consequent of the theorem.

```

T1 T2 T3 z := 1; \qquad \qquad \text{sl.acquire();} \qquad \text{await(z=1);} \\ | | | sl.release(); \qquad | | w := sl.tryAcquire(); \\ | y := z;

```

Fig. 9. Program using spinlock

# 7. Example applications

To demonstrate the application of standard linearizability for proving (or disproving) correctness of concurrent objects, we discuss two typical examples, a spinlock [HS08] and a work-stealing deque [LPCZN13] (the latter developed specifically for ARM). Our soundness result means that whenever an implementation is incorrect with respect to a specification on a given weak memory model, we can use linearizability to prove this. Our completeness result means that whenever an implementation is correct with respect to a specification on a given weak memory model, again we can use linearizability to prove it.

### 7.1. Correctness on TSO

Consider a spinlock object with operations acquire, release and tryAcquire specified as follows.

```

acquire release tryAcquire  \begin{array}{lll} \text{await}(\mathsf{x} := 1); & \mathsf{x} := 1; & \text{if } (\mathsf{x} = 1) \; \mathsf{x} := 0; \; \text{return 1} \\ \mathsf{x} := 0 & \text{else return 0} \end{array}

```

A typical concurrent implementation [HS08] which is correct on SC is

```

acquire release tryAcquire while (true) { x:=1; return TAS(x, 1, 0) while (x=0) {}

```

where TAS(x,a,b) is the atomic hardware primitive test-and-set which, when x is a, sets x to b and returns 1, and otherwise returns 0. The TAS instruction has a built-in fence to ensure any change it makes to x is immediately visible to all threads.

An earlier version of linearizability on TSO [DSD14] proved that this implementation is correct on TSO. However (as discussed in Section 1) it did not require that abstract operations take effect immediately. Under our definition of object refinement (for which we assume abstract operations take effect atomically), it is not correct.

Consider the client program in Figure 9 which contains a triangular race. The program uses a spinlock object sI for which we assume that initially x = 1 and z = 0. Following the operational semantics of TSO in [SSO<sup>+</sup>10], one possible trace of this program is<sup>9</sup>

```

\begin{split} &\langle \mathit{inv}(\mathsf{T2},\mathsf{sl.acquire}), \bot), \mathit{res}((\mathsf{T2},\mathsf{sl.acquire},\bot), \mathit{eff}((\mathsf{T2},\mathsf{sl.acquire}),\bot), \mathit{inv}((\mathsf{T2},\mathsf{sl.release}),\bot), \\ &\mathit{res}(\mathsf{T2},\mathsf{sl.release},\bot), \mathit{step}(\mathsf{T2},\mathsf{y}:=0), \mathit{step}(\mathsf{T1},\mathsf{z}:=1), \mathit{eff}(\mathsf{T1},\mathsf{z}:=1), \mathit{step}(\mathsf{T3},\mathsf{await}(\mathsf{z}=1)), \\ &\mathit{eff}(\mathsf{T3},\mathsf{await}(\mathsf{z}=1)), \mathit{inv}((\mathsf{T3},\mathsf{sl.tryAcquire}),\bot), \mathit{res}((\mathsf{T3},\mathsf{sl.tryAcquire}),0), \mathit{eff}((\mathsf{T3},\mathsf{sl.tryAcquire}),0), \\ &\mathit{step}(\mathsf{T3},\mathsf{w}:=0), \mathit{eff}(\mathsf{T3},\mathsf{w}:=0), \mathit{eff}((\mathsf{T2},\mathsf{sl.release}),\bot), \mathit{eff}(\mathsf{T2},\mathsf{y}:=0) \end{split} ) \end{split}

```

This trace corresponds to thread T2 acquiring and releasing the lock and reading the initial value of z, but not flushing the value written to x by the release operation until after the other two threads have run to completion. The observable behaviour of the trace is

```

\langle \mathit{eff}(\mathsf{T}1, \mathsf{z} := 1), \mathit{eff}(\mathsf{T}3, \mathsf{w} := 0), \mathit{eff}(\mathsf{T}2, \mathsf{y} := 0) \rangle

```

<sup>&</sup>lt;sup>9</sup> The effects in TSO correspond to flushes for program steps and operations which write to global variables, and immediately follow the program step or operation response otherwise.

```

T1 T2

sl.acquire(); sl.acquire();

y := y + 1; y := y + 1;

sl.release() sl.release()

```

Fig. 10. Another program using spinlock

This is not an observable trace of the program running with an abstract object whose effects are not delayed: if y=0 then the step y:=z and hence sl.release on T2 must have occurred before z:=1 on T1, and hence before sl.tryAcquire on T3. Hence, we do not have object refinement. We can prove this with the standard definition of linearizability due to it being sound with respect to object refinement.

The spinlock implementation without the tryAcquire operation is, however, known to be correct on TSO [SSO<sup>+</sup>10]. Again we can show this using our definition of object refinement.

The traces of the implementation derived from the operational semantics of TSO show that if an acquire has responded (and hence has been observed due to the fence in the TAS) then another acquire cannot respond until after a release on the same core has responded or a release on another core has been observed. This coincides with what can be observed from the abstract specification, i.e., an acquire is always followed by a release (before another acquire can occur). Hence, object refinement holds. Again we can prove this with the standard definition of linearizability due to it being complete with respect to object refinement.

#### 7.2. Correctness on ARM and POWER

It is easy to show that the spinlock implementation of Section 7.1, even without the tryAcquire operation, is not correct on ARM and POWER using our definition of object refinement. For example, consider the client program in Figure 10 for which we assume that initially x = 1 and y = 0. Following the operational semantics of ARM and POWER given in [CS18], one possible trace of this program is  $^{10}$

```

\begin{split} &\langle inv((\mathsf{T1},\mathsf{sl.acquire}),\bot), \mathit{res}((\mathsf{T1},\mathsf{sl.acquire}),\bot), \mathit{eff}((\mathsf{T1},\mathsf{sl.acquire}),\bot), \mathit{step}(\mathsf{T1},\mathsf{y} := 1), \\ &inv((\mathsf{T1},\mathsf{sl.release}),\bot), \mathit{res}((\mathsf{T1},\mathsf{sl.release}),\bot), \mathit{eff}((\mathsf{T1},\mathsf{sl.release}),\bot), \mathit{inv}((\mathsf{T2},\mathsf{sl.acquire}),\bot), \\ &\mathit{res}((\mathsf{T2},\mathsf{sl.acquire}),\bot), \mathit{eff}((\mathsf{T2},\mathsf{sl.acquire}),\bot), \mathit{step}(\mathsf{T2},\mathsf{y} := 1), \mathit{inv}((\mathsf{T2},\mathsf{sl.release}),\bot), \mathit{res}((\mathsf{T2},\mathsf{sl.release}),\bot), \\ &\mathit{eff}((\mathsf{T2},\mathsf{sl.release}),\bot), \mathit{eff}(\mathsf{T1},\mathsf{y} := 1), \mathit{eff}(\mathsf{T2},\mathsf{y} := 1)) \end{split}

```

This trace corresponds to the response of T1's release operation being observed before its update to y. This allows T2's acquire to occur followed by its update of y before T1's new value of y is observable by T2. Hence, both threads update y to 1.

Since the observable behaviour  $\langle eff(T1,y:=1), eff(T2,y:=1) \rangle$  of the above trace is not possible using the specification, the implementation is not correct on ARM or POWER: object refinement does not hold. We can prove this with the standard definition of linearizability due to it being sound with respect to object refinement.

# 7.2.1. Chase-Lev deque

As a more substantial example, consider the below code for a version of the Chase-Lev work-stealing deque (double-ended queue) [CL05] developed specifically for ARM [LPCZN13]. The code shown corresponds to a refactoring used in [CS18] which, for example, eliminates returns from within a branch, and for simplicity assumes the elements of the deque are integers.

<sup>&</sup>lt;sup>10</sup> In the operational semantics of [CS18] the placement of effects can be derived from the model of the "storage subsystem" which keeps track of which updates to global variables have been seen by which threads.

```

put(v)

take

steal

int t;

int h,t,task;

int h,t,task;

t := tail;

t := tail-1;

h := head:

tasks[t mod L] := v;

tail := t;

fence;

fence;

fence;

t := tail;

tail := t+1

h := head;

cfence;

if (h \ll t)

if (h < t)

task := tasks[t mod L];

task := tasks[h mod L];

if (h=t)

cfence;

if !CAS(head, h, h + 1) then

if !CAS(head, h, h+1)

task := empty;

task := fail;

tail := tail + 1;

else

task := empty;

task := empty;

return task

tail := tail + 1;

return task

```

The deque is implemented as a circular array of size L with a head and tail pointer. Elements may be *put* on or *taken* from the tail by a worker thread, and additionally, other (thief) processes may *steal* an element from the head of the deque (in order to balance system workload). Since the put and take operations are executed by a single thread, there is no interference between these two operations.

The put operation straightforwardly adds an element to the end of the deque, incrementing the tail pointer. It includes a full fence so that the increment of the tail pointer does not take effect before the element is placed in the array.